Complete FMC Timing Module with IRIG-B, GPS, 1PPS, IEEE1588, SyncE

- FPGA Mezzanine Card (FMC) compatible with VITA 57.1

- Single-module complete timing card supporting grandmaster clock / slave clock modes

- GPS receiver on board

- Sine Wave clock input (typically 10MHz)

- 1PPS/IRIG-B DCLS/Manchester input

- Clock/IRIG-B DCLS/Manchester output

- IRIG-B Amplitude Modulated (AM) input

- IRIG-B Amplitude Modulated (AM) output

- Synchronous Ethernet (SyncE) Master/Slave

- IEEE1588 PTP Master/Slave via 10/100/1000Base-T

- NMEA standard serial output from GPS

- Host board interface for optional communication with FMC carrier board host FPGA

- 5x DPLL on board for precise timekeeping

- RoHS compliant

- FMC160 firmware binaries provided by VadaTech

- Carrier board FPGA reference design sources available

Download Datasheet Add to Info Request

add to compare

The FMC160 is an FPGA Mezzanine Module per VITA 57 specification providing a complete timing solution. The FMC160 has 1PPS, Sine Wave clock, IRIG-B input, IRIG-B out and a GbE.

The module can take its upstream time/frequency from one of:

- GPS (freq and time + location/velocity/other metadata)

- IEEE1588 PTP (freq and time)

- IRIG-B AM/DCLS/Manchester (freq and time)

- 1PPS (freq only)

- Sine Wave Clock In (freq only)

- Synchronous Ethernet (freq only, can be combined with IEEE1588 PTP)

- Carrier board 1PPS via FMC connector (freq only)

The module can provide its downstream time/frequency to all of:

- IEEE1588 PTP (freq and time)

- IRIG-B AM/DCLS/Manchester (freq and time)

- 1PPS (freq only, can be combined with

- NMEA for freq and time) NMEA (time only, can be combined with 1PPS for freq and time)

- Clock Out (freq only)

- Synchronous Ethernet (freq only)

- Carrier board Host interface and clocks via FMC connector

The standard firmware on the FMC160 interfaces to the carrier FPGA through SPI for obtaining time/location/velocity metadata. But additional hardware interfaces are available such as PCIe, Ethernet, Aurora, etc. Contact VadaTech if you have an interest in interfacing to the FMC160 via these additional protocols via the FMC connector.

The module has an on board 5 x DPLL. The DPLL synchronizes 1Hz to 750MHz, providing frequency with jitter cleaning of noisy references. Complies with ITU-T G.8286, G.813, G. 812 and Telcordia GR-253/GR-1244. The module will automatically holdover upon loss of reference while still providing its time/frequency outputs to the rest of the system. The DPLL allows for fast lock to 1HZ input taking only 3 to 60 seconds depending on the reference input compared to 10 minutes or more for previous solutions.

The FMC160 provides standard NMEA format via RS-232 for external devices.

The FMC160 provides synchronized clock to the carrier thru its CLK0 and CLK1. The FMC160 has CLK2 and CLK3 routed to the DPLL as an input reference option. The Module also routes from the DPLL to the LA00/LA17 clock pins.

The FMC160-resident firmware binaries are provided by VadaTech and customer development is not expected for the FMC160 itself. Customer development is expected for the FPGA on the FMC carrier board, but reference design source code will be made available to provide an example of how to interface to the FMC160 host interface (SPI + Clocks/1PPS). The module also interfaces to the carrier with SERDES on DP0/1 as well as DP4/5.

Key Features

- FPGA Mezzanine Card (FMC) compatible with VITA 57.1

- Single-module complete timing card supporting grandmaster clock / slave clock modes

- GPS receiver on board

- Sine Wave clock input (typically 10MHz)

- 1PPS/IRIG-B DCLS/Manchester input

- Clock/IRIG-B DCLS/Manchester output

- IRIG-B Amplitude Modulated (AM) input

- IRIG-B Amplitude Modulated (AM) output

- Synchronous Ethernet (SyncE) Master/Slave

- IEEE1588 PTP Master/Slave via 10/100/1000Base-T

- NMEA standard serial output from GPS

- Host board interface for optional communication with FMC carrier board host FPGA

- 5x DPLL on board for precise timekeeping

- RoHS compliant

- FMC160 firmware binaries provided by VadaTech

- Carrier board FPGA reference design sources available

Benefits

- Design utilizes proven VadaTech subcomponents and engineering techniques

- Electrical, mechanical, software, and system-level expertise in house

- Full system supply from industry leader

Specifications

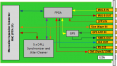

Block diagram

Related News

press release

March 1, 2023

VadaTech announces an FPGA Mezzanine Module per VITA 57 specification providing a complete timing solution. Read More...

AMC585

Zynq UltraScale+ FPGA, FMC+ Carrier, AMC

- Xilinx UltraScale+ XCZU19EG FPGA

- Single FMC+ (VITA 57.4) site

- 8 GB of 64-bit wide DDR4 Memory (single bank) with ECC (CPU)

- 8 GB of 64-bit wide DDR4 Memory (single bank, FPGA)

- MPSoC with block RAM and UltraRAM

- SD Card (option)

- 128 MB of boot Flash

- 64 GB of user Flash

View product

AMC585 Data Sheet

FMC214

70 MHz to 6 GHz Dual Versatile Wideband Transceiver (MIMO), FMC

- Dual complete transceiver signal chain solution using Analog Devices AD9361 transceiver

- Frequency range 70 MHz to 6 GHz with instantaneous bandwidth from 200 kHz to 56 MHz

- MIMO transceiver is Time Domain Duplex (TDD) and Frequency Domain Duplex (FDD) compatible

- Supported by DAQ Series™ data acquisition software

- FPGA Mezzanine Card (FMC) per VITA 57

- Multiplexed 2x RF inputs on each RF channel

- On-board clocking with multi-card synchronization capability

- Low Pin Count (LPC) 160-pin connector

View product

FMC214 Data Sheet

VPX592

FPGA/FMC Carrier, Kintex UltraScale™, 3U VPX

- 3U FPGA carrier for FPGA Mezzanine Card (FMC) per VITA 46 and VITA 57

- Xilinx Kintex UltraScale™ XCKU115 FPGA

- High-performance clock jitter cleaner

- VHDL reference design with source code

- Protocols such as PCIe, SRIO, 10GbE/40GbE, etc. are FPGA programmable

- Compatible with VadaTech and 3rd party FMCs

- 20 GB of DDR4 Memory (2 banks of 64-bit wide, and single bank of 32-bit wide)

- Health Management through dedicated Processor

View product

VPX592 Data Sheet

Info request

Create a list of products to inquire about for more information or quote request.